Ponte Vecchio built on chiplets

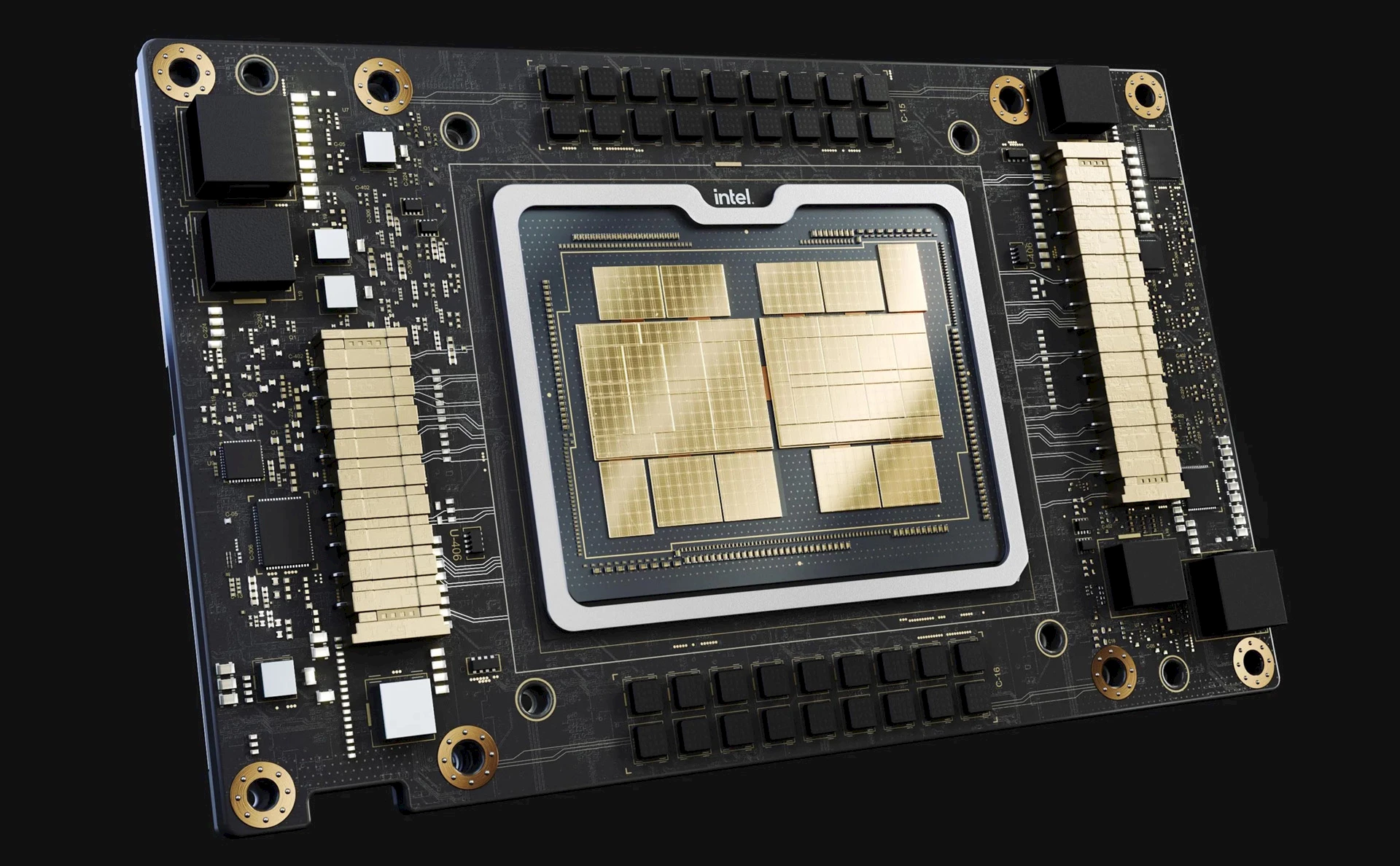

Ponte Vecchio processor. © Intel.

Monday, Intel revealed more details of the processor that will power the Aurora supercomputer, which is designed to become one of the first U.S.-based high-performance computers (HPCs) to break the exaflop barrier of a billion billion high-precision floating-point calculations per second. The Ponte Vecchio processor is a structure that combines several silicon tiles, or chiplets, which are like bricks pieced together. The design is based on Intel’s 2D and 3D chiplet technology where each tile has a dedicated function: calculation, cache, network or memory for example.

Each chiplet may also involve different technologies, making it a prime example of a trend called heterogeneous integration. With this breakthrough, Intel has managed to fit 3,100 mm2 of silicon —equivalent to nearly four Nvidia A100 GPUs — into a 2,330 mm2 space. This represents more than 100 billion transistors spread over 47 pieces of silicon. Quite an achievement.

As a matter of fact, chiplet interconnection standards are in the works, supported by major companies such as Intel, AMD, Qualcomm, ARM, TSMC and Samsung.

⇨ IEEE Spectrum, Samuel K. Moore, “Behind Intel’s HPC chip that will pierce the exascale barrier.”

2022-02-25